- 您现在的位置:买卖IC网 > Sheet目录3833 > PIC16LF84A-04I/SS (Microchip Technology)IC MCU FLASH 1KX14 EE 20SSOP

Micrel, Inc.

KSZ8851SNL/SNLI

August 2009

59

M9999-083109-2.0

Flow Control High Watermark Register (0xB2 – 0xB3): FCHWR

This register is used to control the flow control for high watermark in QMU RX queue.

Bit

Default Value

R/W

Description

15-12

-

RW

Reserved

11-0

0x0300

RW

FCHWC Flow Control High Watermark Configuration

These bits are used to define the QMU RX queue high watermark configuration. It is in

double words count and default is 3.072 KByte available buffer space out of 12 KByte.

Flow Control Overrun Watermark Register (0xB4 – 0xB5): FCOWR

This register is used to control the flow control for overrun watermark in QMU RX queue

Bit

Default Value

R/W

Description

15-12

-

RW

Reserved

11-0

0x0040

RW

FCLWC Flow Control Overrun Watermark Configuration

These bits are used to define the QMU RX queue overrun watermark configuration. It is in

double words count and default is 256 Bytes available buffer space out of 12 Kbyte.

0xB6 – 0xBF: Reserved

Chip ID and Enable Register (0xC0 – 0xC1): CIDER

This register contains the chip ID and the chip enable bit.

Bit

Default

R/W

Description

15-8

0x88

RO

Family ID

Chip family ID

7-4

0x7

RO

Chip ID

0x7 is assigned to KSZ8851SNL

3-1

0x1

RO

Revision ID

0

0x0

RW

Reserved

0xC2 – 0xC5: Reserved

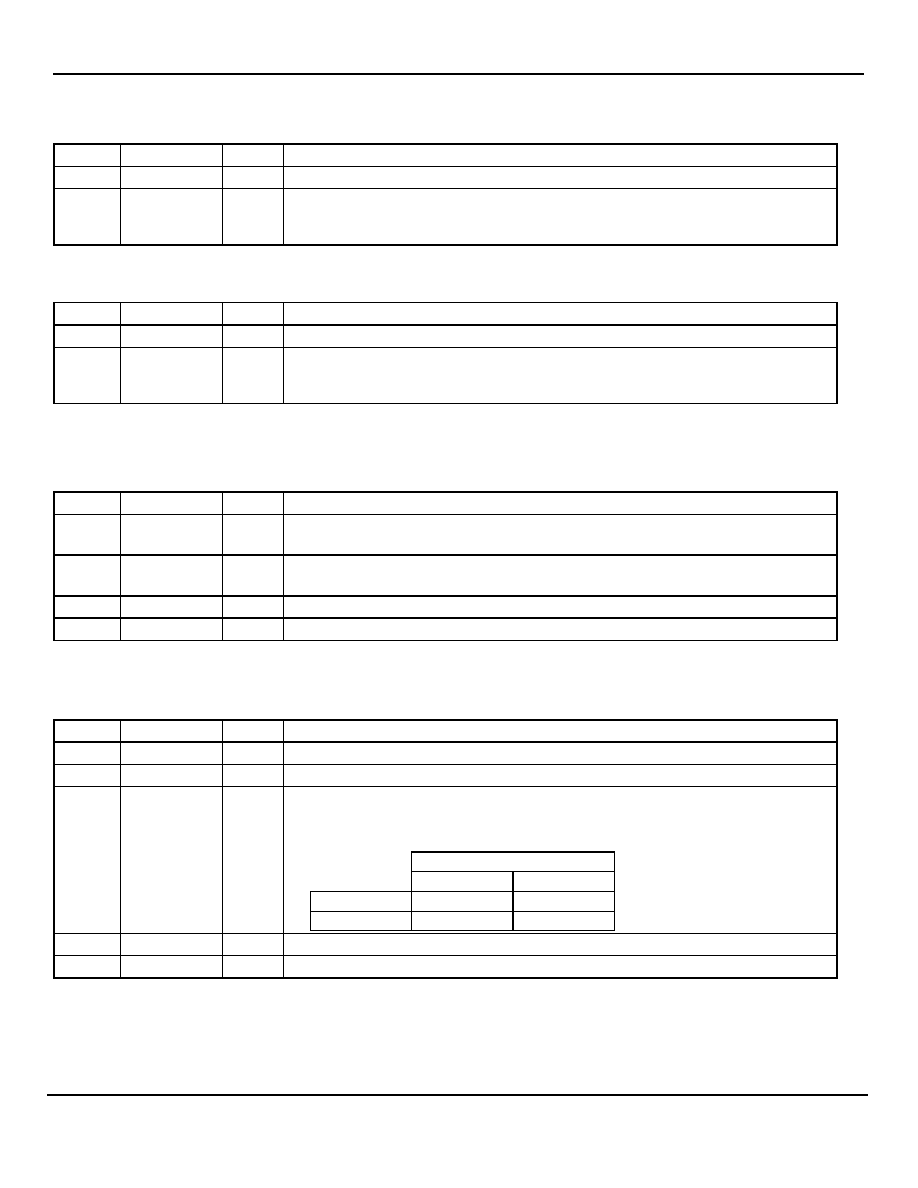

Chip Global Control Register (0xC6 – 0xC7): CGCR

This register contains the global control for the chip function.

Bit

Default

R/W

Description

15-12

0x0

RW

Reserved

11-10

0x2

RW

Reserved

9

0x0

RW

LEDSEL0

This bit sets the LEDSEL0 selection for LED1 and LED0.

PHY port LED indicators, defined as below:

LEDSEL0

0

1

LED1 (pin32)

100BT

ACT

LED0 (pin1)

LINK/ACT

LINK

8

0x0

R/W

Reserved

7-0

0x35

RW

Reserved

Indirect Access Control Register (0xC8 – 0xC9): IACR

This register contains the indirect control for the MIB counter (Write IACR triggers a command. Read access is

determined by bit 12).

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

5176916-1

HIGH CURRENT DRAWER 24P

PIC18F2520-I/SP

IC MCU FLASH 16KX16 28-DIP

PIC18F86J65-I/PT

IC PIC MCU FLASH 48KX16 80TQFP

PIC32MX320F064H-40I/MR

IC PIC MCU FLASH 64KB 64-QFN

PIC18F4423-I/P

IC PIC MCU FLASH 8KX16 40DIP

PIC18LF8390-I/PT

IC PIC MCU FLASH 4KX16 80TQFP

PIC18F2455-I/SO

IC PIC MCU FLASH 12KX16 28SOIC

TS87C51RD2-VCL

IC MCU 8051 OTP 64K 5V 68PLCC

相关代理商/技术参数

PIC16LF84A-04I/SS

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16LF84 SSOP28

PIC16LF84AT-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF870-I/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT